- * 프린트는 Chrome에 최적화 되어있습니다. print

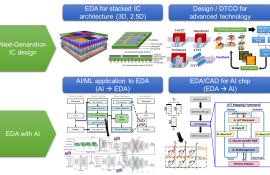

반도체설계자동화 연구실은 시스템온칩 및 고밀도 집적회로의 설계를 위한 컴퓨터이용설계(CAD) 솔루션을 연구합니다. 다양한 디지털 IP 및 칩에 대해 전력, 성능, 면적, 설계 시간 등의 관점에서 가장 효율적으로 설계할 수 있는 전자설계자동화 (EDA) 프레임워크를 구축하는 것을 목표로 연구를 진행하고 있습니다. 현재 (1) 차세대 집적회로 구조(3D, 2.5D, 선단 공정 등)에 대한 EDA 및 (2) 인공지능과의 융합 연구(EDA를 위한 인공지능, 인공지능을 위한 EDA)로 분야를 확장하고 있습니다.

SeDA lab. focuses on researching and developing computer-aided design (CAD) solutions for SoC & VLSI. Our goal is to build electronic design automation (EDA) frameworks for cutting-edge digital IPs/chips with short time-to-market (TTM) and optimized power, performance, area, and cost (PPAC). We are extending our research coverage in the direction of (1) next-generation integrated chip (IC) structures, such as 3D ICs, chiplet-based 2.5D ICs, and under advanced technology nodes; and (2) EDA with AI in both directions: AI for EDA (AI/ML application to EDA) and EDA for AI (EDA framework for AI chip design)

Major research field

Electronic Design Automation & Computer-Aided Design, AI/ML application to EDA

Desired field of research

EDA for 3D & chiplet-based 2.5D ICs, DTCO for advance technology nodes, AI-driven EDA, EDA for AI semiconductor chips

Research Keywords and Topics

Electronic design automation (EDA), Computer-aided design (CAD), 3D IC, 2.5D IC, Design-technology co-optimization (DTCO), AI-EDA, MLCAD, AI chip design

Research Publications

· Gyumin Kim and Heechun Park, "A Unified Design Flow for Homogeneous and Heterogeneous 3D Integration with Fine-Pitch Hybrid Bonding", IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2025

· Junghyun Yoon and Heechun Park, "Mitigating Routability Problems in Complementary-FET-based VLSI Designs", IEEE/ACM Design Automation Conference (DAC), 2025

· Dhoui Lim and Heechun Park, "Timing-Driven Detailed Placement with Unsupervised Graph Learning", IEEE/ACM Design, Automation and Test in Europe Conference (DATE), 2025

Patents

· "심층 신경망을 위한 뉴로모픽 컴퓨팅 구조의 최적화 시스템", 한국, 등록번호 10-2353816, 2022년 1월 17일

· "신호 전달을 위한 주 경로 및 우회 경로를 갖는 집적 회로 및 그것을 포함하는 집적 회로 패키지", 한국, 등록번호 10-2125340, 2020년 6월 16일

국가과학기술표준분류

- ED. 전기/전자

- ED04. 반도체소자·시스템

- ED0407. 설계 Tool

국가기술지도분류

- 정보-지식-지능화 사회 구현

- 010400. 반도체/나노 신소자 기술

녹색기술분류

- 고효율화기술

- 전력효율성 향상

- 324. 전력 IT기술

6T분류

- IT 분야

- 핵심부품

- 010112. 집적회로기술